# **SMP7500**

## **OPEN COLLECTOR DIGITAL I/O MODULE**

## USER'S MANUAL

P/N: 82-0058-000 Released June 8, 2006

VXI Technology, Inc.

2031 Main Street Irvine, CA 92614-6509 (949) 955-1894

VXI Technology, Inc.

## TABLE OF CONTENTS

#### INTRODUCTION

| TABLE OF CONTENTS                                                     |    |

|-----------------------------------------------------------------------|----|

| Certification                                                         |    |

| Warranty                                                              |    |

| Limitation of Warranty                                                |    |

| Restricted Rights Legend                                              |    |

| DECLARATION OF CONFORMITY                                             |    |

| GENERAL SAFETY INSTRUCTIONS                                           |    |

| Terms and Symbols                                                     |    |

| Warnings                                                              |    |

| SUPPORT RESOURCES                                                     | 9  |

| SECTION 1                                                             | 11 |

| INTRODUCTION                                                          | 11 |

| Introduction                                                          |    |

| Features                                                              | 12 |

| Description                                                           | 12 |

| Programming and Data Access                                           | 14 |

| SECTION 2                                                             | 17 |

| PREPARATION FOR USE                                                   |    |

| Introduction                                                          |    |

| Calculating System Power and Cooling Requirements                     | 17 |

| Setting the Chassis Backplane Jumpers                                 |    |

| Setting the Logical Address                                           |    |

| Example 1                                                             |    |

| Example 2                                                             | 19 |

| Selecting the Extended Memory Space                                   | 19 |

| Front Panel Interface Wiring                                          | 20 |

| Hardware Jumper Selection                                             | 21 |

| Hardware Resistor Network Pull-Up Selection                           |    |

| SECTION 3                                                             | 25 |

| Programming                                                           | 25 |

| Introduction                                                          |    |

| Register Access                                                       |    |

| Addressing                                                            |    |

| Description of Registers - A16                                        |    |

| Description of SMIP II Module Registers - A24 / A32 - Extended Memory |    |

| Description of Registers – A24/A32                                    |    |

| Control Register BUSYN Select                                         | 41 |

| Example of a Port Set as an Output                                    | 44 |

| Example of a Port Set as an Input                                     | 46 |

| Example Of A Port Output Write To A Port Input Read                   |    |

| REGISTER ACCESS EXAMPLES                                              | 51 |

| SECTION 4                                                             | 53 |

| COMMAND DICTIONARY                                                    | 53 |

| Terminology                                                           |    |

| SECTION 5                                                             | 55 |

| THEORY OF OPERATION                                                   |    |

| Introduction                                                          |    |

| VXI INTERFACE                                                         |    |

| Device Transfers (Output Mode)                                        | 56 |

|                                                                       |    |

| Direction                       |    |

|---------------------------------|----|

| Clock Enable                    |    |

| Data Load                       |    |

| Device Triggering (TTL Trigger) |    |

| Device Transfers (Read Mode)    |    |

| Direction                       |    |

| Clock Enable                    | 59 |

| Latch Data                      | 61 |

| Read Data                       | 61 |

| INDEX                           | 62 |

#### CERTIFICATION

VXI Technology, Inc. (VTI) certifies that this product met its published specifications at the time of shipment from the factory. VTI further certifies that its calibration measurements are traceable to the United States National Institute of Standards and Technology (formerly National Bureau of Standards), to the extent allowed by that organization's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

The product referred to herein is warranted against defects in material and workmanship for a period of three years from the receipt date of the product at customer's facility. The sole and exclusive remedy for breach of any warranty concerning these goods shall be repair or replacement of defective parts, or a refund of the purchase price, to be determined at the option of VTI.

For warranty service or repair, this product must be returned to a VXI Technology authorized service center. The product shall be shipped prepaid to VTI and VTI shall prepay all returns of the product to the buyer. However, the buyer shall pay all shipping charges, duties, and taxes for products returned to VTI from another country.

VTI warrants that its software and firmware designated by VTI for use with a product will execute its programming when properly installed on that product. VTI does not however warrant that the operation of the product, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The warranty shall not apply to defects resulting from improper or inadequate maintenance by the buyer, buyersupplied products or interfacing, unauthorized modification or misuse, operation outside the environmental specifications for the product, or improper site preparation or maintenance.

VXI Technology, Inc. shall not be liable for injury to property other than the goods themselves. Other than the limited warranty stated above, VXI Technology, Inc. makes no other warranties, express or implied, with respect to the quality of product beyond the description of the goods on the face of the contract. VTI specifically disclaims the implied warranties of merchantability and fitness for a particular purpose.

#### **RESTRICTED RIGHTS LEGEND**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subdivision (b)(3)(ii) of the Rights in Technical Data and Computer Software clause in DFARS 252.227-7013.

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509 U.S.A.

| MANUFACTURER'S ADDRESS       2031 Main Street<br>Irvine, California 92614-6509         PRODUCT NAME       Open Collector Digital I/O Module         MODEL NUMBER(S)       SMP7500         PRODUCT OPTIONS       All         PRODUCT CONFIGURATIONS       All         VXI Technology, Inc. declares that the aforementioned product conforms to the requirements of<br>the Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC)<br>and carries the "CE" mark accordingly. The product has been designed and manufactured<br>according to the following specifications:         SAFETY       EN61010 (2001)         EMC       EN61326 (1997 w/A1:98) Class A<br>CISPR 22 (1997) Class A<br>VCCI (April 2000) Class A<br>VCCI (April 2000) Class A<br>CCES-003 Class A (ANSI C63:4 1992)<br>AS/NZS 3548 (w/A1 & A2:97) Class A<br>FCC Part 15 Subpart B Class A<br>EN 61010-1:2001         The product was installed into a C-size VXI mainframe chassis and tested in a typical configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>DECLARATION OF CONFORMITY</b><br>Declaration of Conformity According to ISO/IEC Guide 22 and EN 45014 |                                                                                                                                                                   |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Irvine, California 92614-6509         PRODUCT NAME       Open Collector Digital I/O Module         MODEL NUMBER(S)       SMP7500         PRODUCT OPTIONS       All         PRODUCT CONFIGURATIONS       All         VXI Technology, Inc. declares that the aforementioned product conforms to the requirements of the Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC) according to the following specifications:         SAFETY       EN61010 (2001)         EMC       EN61326 (1997 w/A1:98) Class A CISPR 22 (1997) Class A VCCI (April 2000) Class A VCCI (April 2000) Class A VCCI (April 2000) Class A CISPR 22 (1997) Class A FCC Part 15 Subpart B Class A EN 61010-1:2001         The product was installed into a C-size VXI mathemet chassis and tested in a typical configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MANUFACTURER'S NAME                                                                                      | VXI Technology, Inc.                                                                                                                                              |  |  |  |

| MODEL NUMBER(S) SMP7500 PRODUCT OPTIONS All PRODUCT CONFIGURATIONS All VXI Technology, Inc. declares that the aforementioned product conforms to the requirements of the Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC) and carries the "CE" mark accordingly. The product has been designed and manufactured according to the following specifications: SAFETY EN61010 (2001) EMC EN61326 (1997 w/A1:98) Class A CISPR 22 (1997) Class A VCC1 (April 2000) Class A ICES-003 Class A ICES-003 Class A ICES-003 Class A FCC Part 15 Subpart B Class A FCC Part 15 Subpart B Class A EN 61010-1:2001 The product was installed into a C-size VXI mainframe chassis and tested in a typical configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MANUFACTURER'S ADDRESS                                                                                   |                                                                                                                                                                   |  |  |  |

| PRODUCT OPTIONS       All         PRODUCT CONFIGURATIONS       All         VXI Technology, Inc. declares that the aforementioned product conforms to the requirements of the Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC) and carries the "CE" mark accordingly. The product has been designed and manufactured according to the following specifications:         SAFETY       EN61010 (2001)         EMC       EN61326 (1997 w/A1:98) Class A CISPR 22 (1997) Class A VCCI (April 2000) Class A ICES-003 Class A (ANSI C63.4 1992) AS/NZS 3548 (w/A1 & A2:97) Class A FCC Part 15 Subpart B Class A EN 61010-1:2001         The product was installed into a C-size VXI mainframe chassis and tested in a typical configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PRODUCT NAME                                                                                             | Open Collector Digital I/O Module                                                                                                                                 |  |  |  |

| PRODUCT CONFIGURATIONS       All         VXI Technology, Inc. declares that the aforementioned product conforms to the requirements of the Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC) and carries the "CE" mark accordingly. The product has been designed and manufactured according to the following specifications:         SAFETY       EN61010 (2001)         EMC       EN61326 (1997 W/A1:98) Class A CISPR 22 (1997) Class A CISPR 23 (1997) Class A CISPR 24 (1997) Class A CISPR | MODEL NUMBER(S)                                                                                          | SMP7500                                                                                                                                                           |  |  |  |

| VXI Technology, Inc. declares that the aforementioned product conforms to the requirements of the Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC) and carries the "CE" mark accordingly. The product has been designed and manufactured according to the following specifications:         SAFETY       EN61010 (2001)         EMC       EN61326 (1997 w/A1:98) Class A CISPR 22 (1997) Class A VCCI (April 2000) Class A ICES-003 Class A (ANSI C63.4 1992) AS/NZS 3548 (w/A1 & A2:97) Class A FCC Part 15 Subpart B Class A EN 61010-1:2001         The product was installed into a C-size VXI mainframe chassis and tested in a typical configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PRODUCT OPTIONS                                                                                          | All                                                                                                                                                               |  |  |  |

| the Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC)<br>and carries the "CE" mark accordingly. The product has been designed and manufactured<br>according to the following specifications:<br>SAFETY EN61010 (2001)<br>EMC EN61326 (1997 w/A1:98) Class A<br>CISPR 22 (1997) Class A<br>VCCI (April 2000) Class A<br>ICES-003 Class A (ANSI C63.4 1992)<br>AS/NZS 3548 (w/A1 & A2:97) Class A<br>FCC Part 15 Subpart B Class A<br>EN 61010-1:2001<br>The product was installed into a C-size VXI mainframe chassis and tested in a typical configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PRODUCT CONFIGURATIONS                                                                                   | All                                                                                                                                                               |  |  |  |

| EMC EN61326 (1997 w/A1:98) Class A<br>CISPR 22 (1997) Class A<br>VCCI (April 2000) Class A<br>ICES-003 Class A (ANSI C63.4 1992)<br>AS/NZS 3548 (w/A1 & A2:97) Class A<br>FCC Part 15 Subpart B Class A<br>EN 61010-1:2001<br>The product was installed into a C-size VXI mainframe chassis and tested in a typical configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | the Low Voltage Directive 73/23/EEC and the land carries the "CE" mark accordingly. The                  | EMC Directive 89/366/EEC (inclusive 93/68/EEC)                                                                                                                    |  |  |  |

| CISPR 22 (1997) Class A<br>VCCI (April 2000) Class A<br>ICES-003 Class A (ANSI C63.4 1992)<br>AS/NZS 3548 (w/A1 & A2:97) Class A<br>FCC Part 15 Subpart B Class A<br>EN 61010-1:2001<br>The product was installed into a C-size VXI mainframe chassis and tested in a typical configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SAFETY                                                                                                   | EN61010 (2001)                                                                                                                                                    |  |  |  |

| I hereby declare that the aforementioned product has been designed to be in compliance with the relevant sections<br>of the specifications listed above as well as complying with all essential requirements of the Low Voltage Directive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EMC                                                                                                      | CISPR 22 (1997) Class A<br>VCCI (April 2000) Class A<br>ICES-003 Class A (ANSI C63.4 1992)<br>AS/NZS 3548 (w/A1 & A2:97) Class A<br>FCC Part 15 Subpart B Class A |  |  |  |

| of the specifications listed above as well as complying with all essential requirements of the Low Voltage Directive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | The product was installed into a C-size VXI main                                                         | nframe chassis and tested in a typical configuration.                                                                                                             |  |  |  |

| June 2006                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |                                                                                                                                                                   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | June 2006                                                                                                |                                                                                                                                                                   |  |  |  |

| Steve Mauga, QA Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CE                                                                                                       | Steve Mauga, QA Manager                                                                                                                                           |  |  |  |

### **GENERAL SAFETY INSTRUCTIONS**

Review the following safety precautions to avoid bodily injury and/or damage to the product. These precautions must be observed during all phases of operation or service of this product. Failure to comply with these precautions, or with specific warnings elsewhere in this manual, violates safety standards of design, manufacture, and intended use of the product.

Service should only be performed by qualified personnel.

#### TERMS AND SYMBOLS

These terms may appear in this manual:

| WARNING | Indicates that a procedure or condition may cause bodily injury or death.                         |  |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| CAUTION | Indicates that a procedure or condition could possibly cause damage to equipment or loss of data. |  |  |  |  |  |  |  |  |

These symbols may appear on the product:

**ATTENTION - Important safety instructions**

Frame or chassis ground

Indicates that the product was manufactured after August 13, 2005. This mark is placed in accordance with *EN 50419*, *Marking of electrical and electronic equipment in accordance with Article 11(2) of Directive 2002/96/EC (WEEE)*. End-of-life product can be returned to VTI by obtaining an RMA number. Fees for take-back and recycling will apply if not prohibited by national law.

#### WARNINGS

Follow these precautions to avoid injury or damage to the product:

| Use Proper Power Cord   | To avoid hazard, only use the power cord specified for this product.                                                                      |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Use Proper Power Source | To avoid electrical overload, electric shock, or fire hazard, do not<br>use a power source that applies other than the specified voltage. |

| Use Proper Fuse         | To avoid fire hazard, only use the type and rating fuse specified for this product.                                                       |

#### WARNINGS (CONT.)

| Avoid Electric Shock | To avoid electric shock or fire hazard, do not operate this product<br>with the covers removed. Do not connect or disconnect any cable,<br>probes, test leads, etc. while they are connected to a voltage source.<br>Remove all power and unplug unit before performing any service.<br><i>Service should only be performed by qualified personnel.</i>                                                                                                                     |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ground the Product   | This product is grounded through the grounding conductor of the<br>power cord. To avoid electric shock, the grounding conductor must<br>be connected to earth ground.                                                                                                                                                                                                                                                                                                       |

| Operating Conditions | <ul> <li>To avoid injury, electric shock or fire hazard:</li> <li>Do not operate in wet or damp conditions.</li> <li>Do not operate in an explosive atmosphere.</li> <li>Operate or store only in specified temperature range.</li> <li>Provide proper clearance for product ventilation to prevent overheating.</li> <li>DO NOT operate if any damage to this product is suspected. <i>Product should be inspected or serviced only by qualified personnel.</i></li> </ul> |

| Improper Use         | The operator of this instrument is advised that if the equipment is<br>used in a manner not specified in this manual, the protection<br>provided by the equipment may be impaired.<br>Conformity is checked by inspection.                                                                                                                                                                                                                                                  |

### **SUPPORT RESOURCES**

Support resources for this product are available on the Internet and at VXI Technology customer support centers.

VXI Technology World Headquarters

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509

Phone: (949) 955-1894 Fax: (949) 955-3041

#### VXI Technology Cleveland Instrument Division

5425 Warner Road Suite 13 Valley View, OH 44125

Phone: (216) 447-8950 Fax: (216) 447-8951

#### VXI Technology Lake Stevens Instrument Division

VXI Technology, Inc. 1924 - 203 Bickford Snohomish, WA 98290

Phone: (425) 212-2285 Fax: (425) 212-2289

#### **Technical Support**

Phone: (949) 955-1894 Fax: (949) 955-3041 E-mail: support@vxitech.com

Visit http://www.vxitech.com for worldwide support sites and service plan information.

VXI Technology, Inc.

## **SECTION 1**

### INTRODUCTION

#### INTRODUCTION

The SMP7500 is a high-performance I/O module that has been designed for high data throughput and flexibility of configuration. The instrument uses direct register access for very high-speed data input and retrieval.

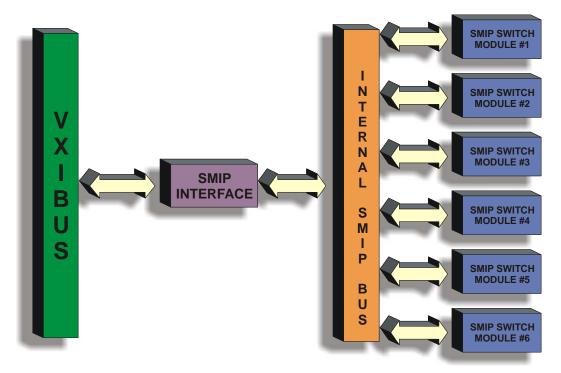

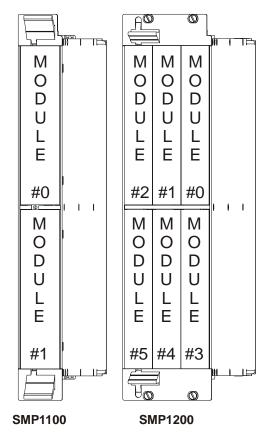

The SMP7500 is a member of the VXI Technology SMIP  $II^{\text{TM}}$  (*Switch Modularity Instrumentation Platform*) family and is available as a 96-channel, single SMIP Plug-In Module. As many as six SMP7500s may be configured in a single double-slot VXI module, and 2 in a single-wide VXI module. This would allow as many as 576 for a double-wide or 192 digital I/O for a single-wide VXI Module. In addition, the SMP7500 may be combined with any of the other members of the SMIP family to form a customized and highly integrated instrument/switch test solution. This allows the user to reduce system size and cost by combining the SMP7500 with another instrument/switch function in a single wide, C-size VXIbus module.

FIGURE 1-1: SMIP<sup>TM</sup> SWITCH MODULARITY INSTRUMENTATION PLATFORM

Regardless of whether the SMP7500 is configured with other SMP7500 modules or with other SMIP *II* modules, each group of 96 channels is treated as an independent plug-in in the SMIP *II* module and as such, each group has its own FAIL/POWER and ACCESS/ERROR indicators.

FIGURE 1-2: FRONT PANEL LAYOUT

#### **FEATURES**

- 96 Channels, 12 groups of 8 bits. Up to 576 channels in a double-slot C-size card, up to 192 channels in a single C-size card.

- Group-wise programmable, as an input or an output, through user TTL input or VXI A24/32 registers.

- Group-wise programmable polarity through VXI A24/32 registers as an active high or low.

- Input: 0 V to 60 V,  $V_{IN \text{ (high)}} \ge 2.0 \text{ V}$ ,  $V_{IN(low)} \le 1.5 \text{ V}$ , input impedance  $\ge 65 \text{ k}\Omega$ .

- Output: Open collector (N-DMOS), 0 V to 60 V, up to 300 mA continuous with over-voltage and over-current protection.

- Data throughput: 5 µs typical system speeds, 200 kilobytes per second (kb/s) using D8 access, 400 kb/s using D16 access.

- Data Input/Output Clock Sources: For each group, from Front Panel (F/P) clock input, or VXI Register Writes.

- Capture clock edge programmable as rising edge or falling edge.

- Register based data access for fast throughput.

#### DESCRIPTION

The SMP7500 Open Collector Digital I/O module is a high performance I/O module that has been designed for high voltage, current and data throughput. The instrument uses direct register access for very high-speed data through-put.

A single SMP7500 provides 96 open collector digital I/O line that are configurable as inputs or outputs in twelve groups of 8 channels each. The module can drive up to 60 V with sink current of up to 300 mA per channel. Each group of 8 bits is referred as a PORT. Each PORT can be configured as an input port or an output port under program control. The SMP7500 has the flexibility to configure the sourcing of the input and output clocks from either the front panel (F/P GND\_I/O) (one input per PORT), or via a VXI A24/A32 control register. There is also a Global Clock Line from the front panel that may be user selected via hardware jumpers to drive selected PORT clocks. By using the appropriate clocking configuration, very large numbers of channels may by synchronized to collect or present data to a UUT (unit under test).

Each clock input is internally pulled to a logic high level and has an RC termination network to reduce multiple clocking edges due to line ringing. The RC network consists of a 120  $\Omega$  resistor in series with a 100 pF capacitor, giving a time constant of 12 ns.

The SMP7500 can be combined with any member of the SMIP *II* family to form a customized and highly integrated instrument/switch.

#### **PROGRAMMING AND DATA ACCESS**

#### **Register-based Data Access:**

The I/O ports are directly mapped into the VXI user definable registers in the A24 or A32 address space. Data access occurs in approximately 500 ns, depending on the controller and software used.

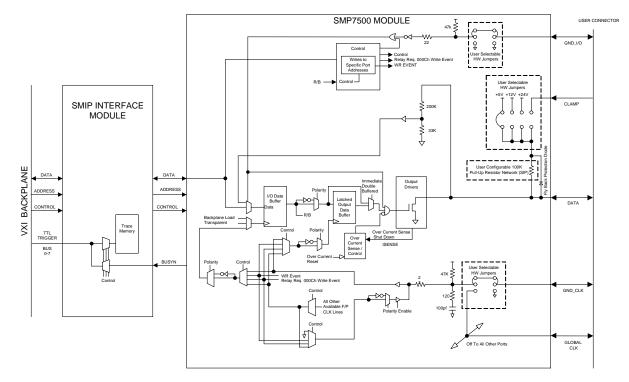

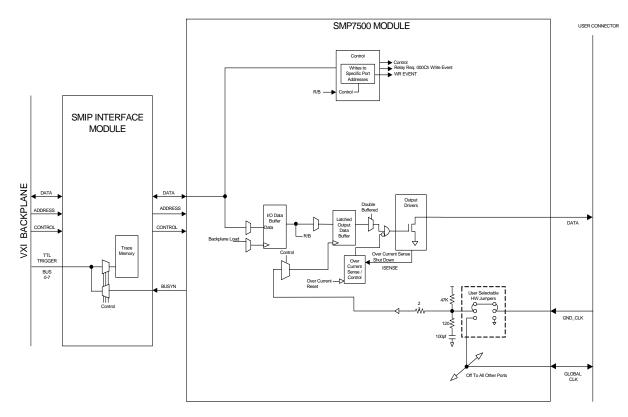

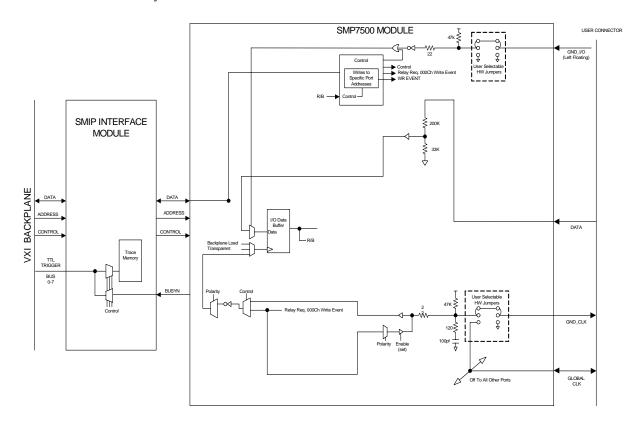

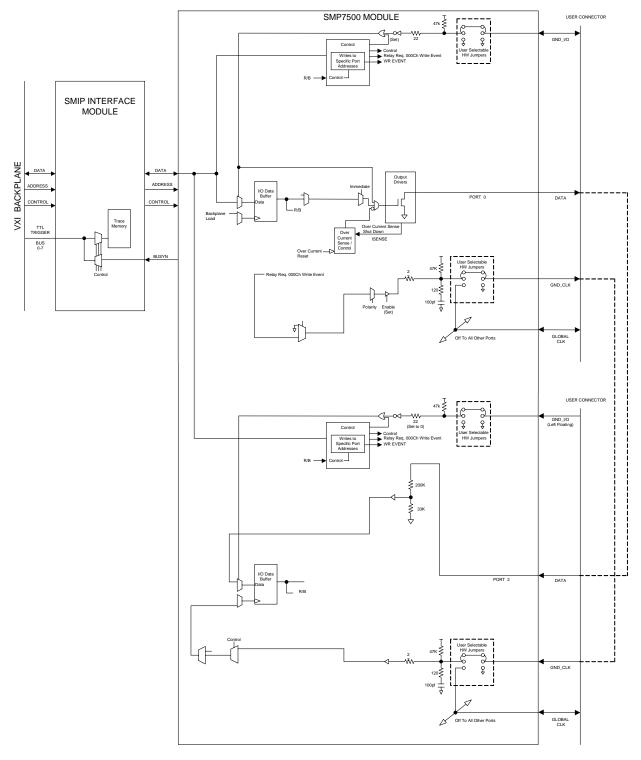

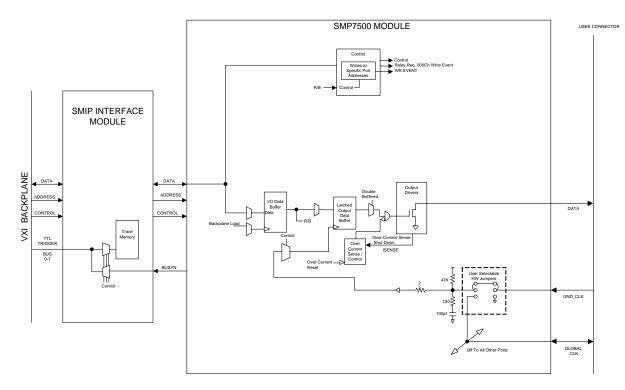

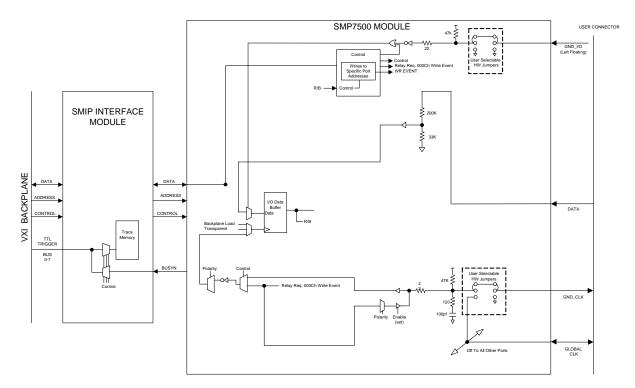

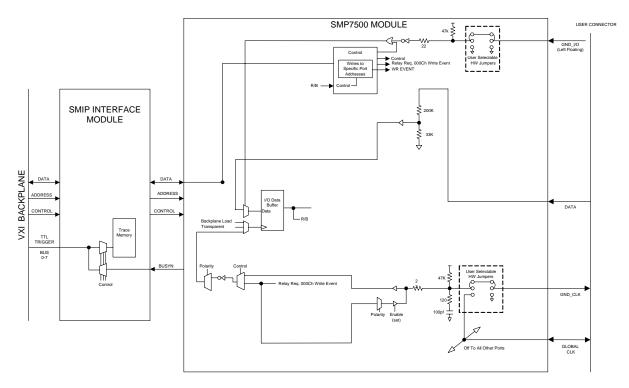

FIGURE 1-3: SMP7500 MODULE BLOCK DIAGRAM

#### **SMP7500 SPECIFICATIONS**

| GENERAL SPECIFICATIONS                  |                                                                               |

|-----------------------------------------|-------------------------------------------------------------------------------|

| NUMBER OF CHANNELS                      |                                                                               |

|                                         | 96 (12 groups of 8 bits)                                                      |

| DIRECTION                               |                                                                               |

|                                         | Selectable as input or output                                                 |

| DATA ACCESS TYPES                       | · ·                                                                           |

|                                         | Direct register access                                                        |

| DATA THROUGHPUT                         |                                                                               |

|                                         | 5 μs typical system (500 μs register cycle time)                              |

|                                         | 200 kb/s using D8 access                                                      |

|                                         | 400 kb/ using D16 access                                                      |

| PHYSICAL INTERFACE                      |                                                                               |

|                                         | N channel DMOS transistor (TPIC2601KTC) with a current protection circuit     |

|                                         | on the output side, and a voltage divider and voltage comparator on the input |

|                                         | side                                                                          |

| CHANNEL INPUT CHARACTERIST              |                                                                               |

| $\mathbf{V_{IN(high)}}$                 | $\geq$ 2.0 V                                                                  |

| $V_{IN(low)}$                           | $\leq$ 1.5 V                                                                  |

| V <sub>IN(max)</sub>                    | $\leq$ 60 V                                                                   |

| Input Impedance                         | $\geq$ 65 k $\Omega$                                                          |

| CHANNEL OUTPUT CHARACTERIS              |                                                                               |

| V <sub>OUT(max)</sub>                   | $\leq 60 \text{ V}$                                                           |

| Current Sink (Maximum)                  | $\leq$ 300 mA                                                                 |

| Switch On Time                          | $\leq 1 \ \mu s$                                                              |

| CLOCK AND CONTROL INPUT CH              |                                                                               |

| $\mathbf{V_{IN(high)}}$                 | > 2.0 V                                                                       |

| V <sub>IN(low)</sub>                    | < 0.8 V                                                                       |

| Current In ( $V_{IN} = 5.0 \text{ V}$ ) | < 10 µA                                                                       |

| DATA INPUT CLOCK SOURCES                |                                                                               |

|                                         | 12 Front Panel, plus 1 Global Clock, A24/A32 Register Write                   |

| DATA OUTPUT CLOCK SOURCES               |                                                                               |

|                                         | 12 Front Panel, A24/A32 Register Write                                        |

| TTL TRIGGER OUTPUT SOURCES              |                                                                               |

|                                         | Board Busyn controlled                                                        |

| CLOCKED INPUT DATA HOLD                 |                                                                               |

|                                         | $\geq 2 \ \mu s$                                                              |

| Down Drown way                          |                                                                               |

| POWER REQUIREMENTS                      |                                                                               |

| POWER REQUIREMENTS                      | +5 V @ 864 mA, +12 V @ 60 mA                                                  |

| COOLING REQUIREMENTS                    |                                                                               |

|                                         | +5 V @ 864 mA, +12 V @ 60 mA<br>0.4 L/s                                       |

VXI Technology, Inc.

## **SECTION 2**

## **PREPARATION FOR USE**

#### INTRODUCTION

When the SMP7500 is unpacked from its shipping carton, the contents should include the following items:

- (1) SMP7500 VXIbus module

- (1) SMP7500 Open Collector Digital I/O Module User's Manual (this manual)

All components should be immediately inspected for damage upon receipt of the unit.

Once the SMIP *II* is assessed to be in good condition, it may be installed into an appropriate C-size or D-size VXIbus chassis in any slot other than slot zero. The chassis should be checked to ensure that it is capable of providing adequate power and cooling for the SMIP *II*. Once the chassis is found adequate, the SMIP *II*'s logical address and the chassis' backplane jumpers should be configured prior to the SMIP *II*'s installation.

#### **CALCULATING SYSTEM POWER AND COOLING REQUIREMENTS**

It is imperative that the chassis provide adequate power and cooling for this module. Referring to the chassis operation manual, confirm that the power budget for the system (the chassis and all modules installed therein) is not exceeded and that the cooling system can provide adequate airflow at the specified backpressure.

It should be noted that if the chassis cannot provide adequate power to the module, the instrument might not perform to specification or possibly not operate at all. In addition, if adequate cooling is not provided, the reliability of the instrument will be jeopardized and permanent damage may occur. Damage found to have occurred due to inadequate cooling could also void the warranty of the module.

#### SETTING THE CHASSIS BACKPLANE JUMPERS

Please refer to the chassis operation manual for further details on setting the backplane jumpers.

#### SETTING THE LOGICAL ADDRESS

The logical address of the SMIP *II* is set by two rotary switches located on the top edge of the interface card, near the backplane connectors. Each switch is labeled with positions 0 through F. The switch closer to the front panel of the module is the least significant bit (**LSB** or "**Front**"), and the switch located towards the back of the module is the most significant bit (**MSB** or "**Back**"). To set the Logical Address (LA), simply rotate the pointer to the desired value. For example, to set the **LA** to **25**, first convert the decimal number to the hexadecimal value of **19**. Next, set the back switch to **1**, and the front switch to **9**. See Figure 2-1. Here are a couple of conversion examples:

#### Example 1

| LA<br>(decimal) | Divide<br>by 16 |   | MSB             | LSB           |                                                                             |

|-----------------|-----------------|---|-----------------|---------------|-----------------------------------------------------------------------------|

| 25              | 25 / 16         | = | 1               | w/9 remaining | Divide the decimal value by 16 to get the MSB and the LSB.                  |

|                 |                 | = | 0001            | 1001          | <i>The 1 is the MSB, and the remainder of 9 is the LSB.</i>                 |

|                 |                 | = | 1               | 9             | Convert to hexadecimal. Set the back switch to 1 and the front switch to 9. |

|                 |                 |   | BAC             | СК            | FRONT                                                                       |

|                 |                 |   | 2 <sup>34</sup> | 5 6 1 8 9     | 23456<br>189                                                                |

FIGURE 2-1: LOGICAL ADDRESS EXAMPLE 1

000

Here is another way of looking at the conversion:

LA = (back switch x 16) + front switch LA = (1 x 16) + 9LA = 16 + 9LA = 25

008

| Example 2       |                 |   |                                                                                                |               |                                                                                                      |

|-----------------|-----------------|---|------------------------------------------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------|

| LA<br>(decimal) | Divide<br>by 16 |   | MSB                                                                                            | LSB           |                                                                                                      |

| 200             | 200 / 16        | = | 12                                                                                             | w/8 remaining | Divide by 16.                                                                                        |

|                 |                 | = | 1100                                                                                           | 1000          | Convert to MSB and LSB.                                                                              |

|                 |                 | = | C                                                                                              | 8             | Convert to hexadecimal. Set the back switch to C and the front switch to 8.                          |

|                 |                 |   | BAC                                                                                            | K             | FRONT                                                                                                |

|                 |                 |   | 2 <sup>345</sup><br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10 | 0 1 8 9 A A   | 23450<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8 |

FIGURE 2-2: LOGICAL ADDRESS EXAMPLE 2

Set the address switches to **FF** (factory default) for dynamic configuration. Upon power-up, the resource manager will assign a logical address. See Section F - Dynamic Configuration in the *VXIbus Specification* for further information.

There is only one logical address per SMIP *II* base unit. Address assignments for individual modules are handled through the A24/A32 address space allocation.

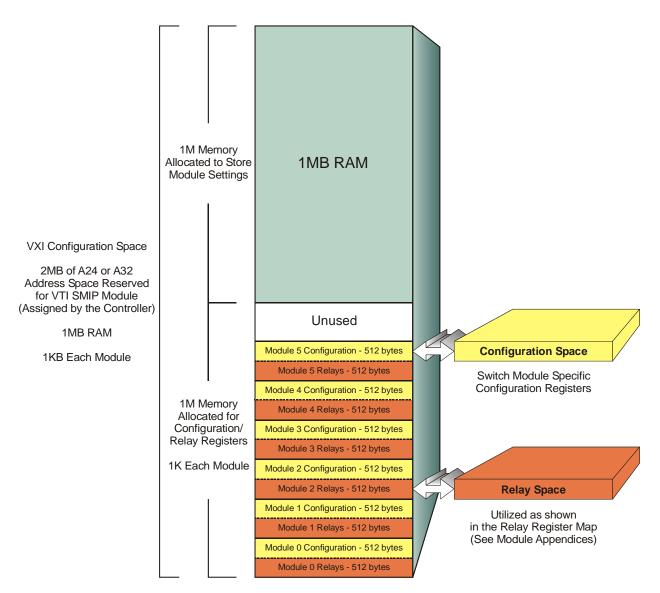

#### SELECTING THE EXTENDED MEMORY SPACE

The Extended Memory Space of the SMIP *II* is set by a dip-switch that is located on the bottom edge of the interface card. Position 1, located to the left on the dip-switch, selects between A24 and A32 memory address space. In the UP position, the SMIP *II* will request A24 space. In the DOWN position, the SMIP *II* will request A32 space. (Position 2 is not currently used.) The selection of the address space should be based upon the memory allocation requirements of the system that the SMIP *II* module will be installed. The amount of memory allocated to the SMIP *II* module is independent of the address space selected.

#### FRONT PANEL INTERFACE WIRING

The SMP7500's module interface is made available on the front panel of the instrument. The 160-pin connector contains all of the signals available for this instrument. The connector used on the SMP7500 is a readily available 160-pin 5 row DIN type connector. Many mating options are available for this connector style, anything from crimp-and-poke to screw terminal connections. Several cable shroud options are also available.

| ROW<br>A | SIGNAL  | ROW<br>B | SIGNAL  | ROW<br>C | SIGNAL   | ROW<br>D | SIGNAL     | ROW<br>E | SIGNAL     |

|----------|---------|----------|---------|----------|----------|----------|------------|----------|------------|

| 1        | DATA0.0 | 1        | DATA2.0 | 1        | DATA4.0  | 1        | CLAMP0     | 1        | CLAMP1     |

| 2        | DATA0.1 | 2        | DATA2.1 | 2        | DATA4.1  | 2        | GND/CLK0   | 2        | GND/CLK1   |

| 3        | DATA0.2 | 3        | DATA2.2 | 3        | DATA4.2  | 3        | GND/IO0    | 3        | GND/IO1    |

| 4        | DATA0.3 | 4        | DATA2.3 | 4        | DATA4.3  | 4        | GND        | 4        | GND        |

| 5        | DATA0.4 | 5        | DATA2.4 | 5        | DATA4.4  | 5        | CLAMP2     | 5        | CLAMP3     |

| 6        | DATA0.5 | 6        | DATA2.5 | 6        | DATA4.5  | 6        | GND/CLK2   | 6        | GND/CLK3   |

| 7        | DATA0.6 | 7        | DATA2.6 | 7        | DATA4.6  | 7        | GND/IO2    | 7        | GND/IO3    |

| 8        | DATA0.7 | 8        | DATA2.7 | 8        | DATA4.7  | 8        | GND        | 8        | GND        |

| 9        | DATA1.0 | 9        | DATA3.0 | 9        | DATA5.0  | 9        | CLAMP4     | 9        | CLAMP5     |

| 10       | DATA1.1 | 10       | DATA3.1 | 10       | DATA5.1  | 10       | GND/CLK4   | 10       | GND/CLK5   |

| 11       | DATA1.2 | 11       | DATA3.2 | 11       | DATA5.2  | 11       | GND/IO4    | 11       | GND/IO5    |

| 12       | DATA1.3 | 12       | DATA3.3 | 12       | DATA5.3  | 12       | GND        | 12       | GND        |

| 13       | DATA1.4 | 13       | DATA3.4 | 13       | DATA5.4  | 13       | CLAMP6     | 13       | CLAMP7     |

| 14       | DATA1.5 | 14       | DATA3.5 | 14       | DATA5.5  | 14       | GND/CLK6   | 14       | GND/CLK7   |

| 15       | DATA1.6 | 15       | DATA3.6 | 15       | DATA5.6  | 15       | GND/IO6    | 15       | GND/IO7    |

| 16       | DATA1.7 | 16       | DATA3.7 | 16       | DATA5.7  | 16       | GND        | 16       | GND        |

| 17       | DATA6.0 | 17       | DATA8.0 | 17       | DATA10.0 | 17       | CLAMP8     | 17       | CLAMP9     |

| 18       | DATA6.1 | 18       | DATA8.1 | 18       | DATA10.1 | 18       | GND/CLK8   | 18       | GND/CLK9   |

| 19       | DATA6.2 | 19       | DATA8.2 | 19       | DATA10.2 | 19       | GND/IO8    | 19       | GND/IO9    |

| 20       | DATA6.3 | 20       | DATA8.3 | 20       | DATA10.3 | 20       | GND        | 20       | GND        |

| 21       | DATA6.4 | 21       | DATA8.4 | 21       | DATA10.4 | 21       | CLAMP10    | 21       | CLAMP11    |

| 22       | DATA6.5 | 22       | DATA8.5 | 22       | DATA10.5 | 22       | GND/CLK 10 | 22       | GND/CLK 11 |

| 23       | DATA6.6 | 23       | DATA8.6 | 23       | DATA10.6 | 23       | GND/IO10   | 23       | GND/IO11   |

| 24       | DATA6.7 | 24       | DATA8.7 | 24       | DATA10.7 | 24       | GND        | 24       | GND        |

| 25       | DATA7.0 | 25       | DATA9.0 | 25       | DATA11.0 | 25       | GND        | 25       | GND/GCLK   |

| 26       | DATA7.1 | 26       | DATA9.1 | 26       | DATA11.1 | 26       | GND        | 26       | GND        |

| 27       | DATA7.2 | 27       | DATA9.2 | 27       | DATA11.2 | 27       | GND        | 27       | GND        |

| 28       | DATA7.3 | 28       | DATA9.3 | 28       | DATA11.3 | 28       | GND        | 28       | GND        |

| 29       | DATA7.4 | 29       | DATA9.4 | 29       | DATA11.4 | 29       | GND        | 29       | GND        |

| 30       | DATA7.5 | 30       | DATA9.5 | 30       | DATA11.5 | 30       | GND        | 30       | GND        |

| 31       | DATA7.6 | 31       | DATA9.6 | 31       | DATA11.6 | 31       | GND        | 31       | GND        |

| 32       | DATA7.7 | 32       | DATA9.7 | 32       | DATA11.7 | 32       | GND        | 32       | GND        |

#### TABLE 2-1: J100 PIN OUTS

#### HARDWARE JUMPER SELECTION

The SMP7500 module contains many user selectable hardware jumpers. The jumpers are of the 2-pin finger removable type found on most personal computers and hard disk drives. These jumpers set the fly-back protection voltage, the functionality of the front panel (F/P) GND\_I/O, GND\_CLK and Global CLK lines, as well as the direction of the PORTs. The Table 2-2 below shows the appropriate jumper settings for the module setup desired.

#### Front Panel CLAMP Lines

The F/P CLAMP lines are available for user defined voltages that are to be used to suppress inductive fly-back transients on the PORT lines. This helps protect other circuitry on the PORT's data lines from an over-voltage condition. The F/P CLAMP line is only one of several sources that may be selected to drive the fly-back protection diodes that are installed on the module. Hardware selectable jumpers on the module can also be used to select either +24 V dc, +12 V dc, or +5 V dc. The voltage selected is routed to the cathode of a fly-back protection diode, whose anode is then connected to the associated PORT's data line. Every PORT data line has a fly-back protection diode installed. If no protection voltage is desired, simply hardware jumper the clamp voltage to the F/P CLAMP line and do not connect that line to any voltage.

#### Front Panel GND\_I/O Lines

The F/P GND\_I/O lines may be configured as either GrouND, or an input line that controls the direction of the associated PORT. If used as inputs the F/P GND\_I/O lines are pulled-up to +5 V via a 47 k $\Omega$  resistor. If these lines are configured as input control lines and are not driven low, they will pull-up setting the associated port as an input. If pulled low, they will set the port to an output. All F/P GND\_I/O lines may be overridden either by a hardware jumper setting or programmatically to set the port direction to output.

If set to GrouND, these lines can be used as additional user employable Ground pins to the module. This increases the user attachments to the system's ground. For high speed switching of many simultaneous channels it may be necessary to use these pins as ground in order to reduce signal bounce caused by switching transients. If these lines are used as GND, and they are not overridden, then they are internally pulled-up and set the PORT's direction as input.

There are two ways to override the F/P GND\_I/O lines. A hardware jumper may be used to select the PORT as an output, or the PORT may be programmatically set to an output. If these lines are overridden, then they have no effect on the module.

#### Front Panel GND\_CLK Lines

The F/P GND\_CLK lines may be configured as either GrouND, an input line, or an output line that controls data capture of the associated PORT. If used as inputs the F/P GND\_CLK lines are pulled-up to +5 V via a 47 k $\Omega$  resistor. There is as well a network of a 120  $\Omega$  resistor in series with a 100 pF capacitor for termination of the F/P\_CLK lines. The polarity of the clock lines are programmable as well.

If set to GrouND, they can be used as additional user employable Ground pins to the module. This increases the user attachments to the system's ground. For high speed switching of many simultaneous channels it may be necessary to use these pins as ground in order to reduce signal bounce caused by switching transients.

A Global CLK Line is available on the front panel. This line is to be used to gang several, or all, PORT clock lines into a single source/destination. The Global CLK line is routed to the required PORTs via hardware jumpers. If a PORT is configured to use the Global CLK line, then its associated F/P GND\_CLK line has no effect on the module.

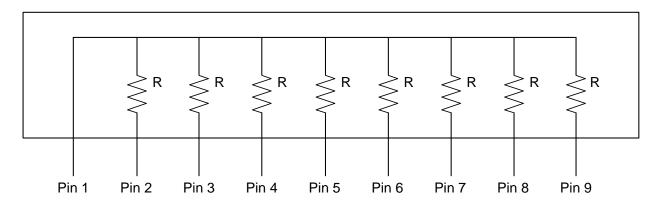

#### HARDWARE RESISTOR NETWORK PULL-UP SELECTION

The SMP7500 module contains user selectable hardware resistor networks that are used to pull-up the F/P data lines to the selected CLAMP voltage. The networks are of the 9-pin 8-resistor single-in-line (SIP) type. Examples of this type of resistor network are:

```

Dale Electronics, IncCSC09A01104G (100 k\Omega)BI TechnologiesBH9-1104 (100 k\Omega)

```

FIGURE 2-3: RESISTOR NETWORK 9P8R SIP

The values of these resistor networks may be selected and the networks replaced per customer requirements. Care should be taken to follow the power rating of the networks selected and the application voltage used so as not to create a potentially dangerous situation. VXI Technology, Inc. does not carry other values of these resistor networks.

#### Front Panel CLAMP Lines

The F/P CLAMP lines are available for user defined voltages that are to be used to suppress inductive fly-back transients on the PORT lines. This helps protect other circuitry on the PORT's data lines from an over-voltage condition. The F/P CLAMP line is only one of several sources that may be selected to drive the fly-back protection diodes that are installed on the module. Hardware selectable jumpers on the module can also be used to select either +24 VDC, +12 VDC, or +5 VDC. The voltage selected is routed to the cathode of a fly-back protection diode, whose anode is then connected to the associated PORT's data line. Every PORT data line has a fly-back protection diode installed. If no protection voltage is desired, simply hardware jumper the clamp voltage to the F/P CLAMP line and do not connect that line to any voltage.

| HARDWARE JUMPERS INSTALLED (HW = HARD WIRED via JUMPER) |                                                    |                                                    |                                                    |                                                    |                                              |                                              |  |  |

|---------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------|----------------------------------------------|--|--|

| FUNCTION                                                | PORT 0                                             | PORT 1                                             | PORT 2                                             | PORT 3                                             | PORT 4                                       | PORT 5                                       |  |  |

| $GND_I/O = GND$                                         | J1 – 1 to 2                                        | J7 – 1 to 2                                        | J14 – 1 to 2                                       | J11 – 1 to 2                                       | J22 – 1 to 2                                 | J19 – 1 to 2                                 |  |  |

| $GND_I/O = I/0 *$                                       | J1 - 2  to  3<br>J2 - 2  to  3                     | J7 – 2 to 3<br>J6 – 2 to 3                         | J14 – 2 to 3<br>J13 – 2 to 3                       | J11 - 2  to  3<br>J10 - 2  to  3                   | J22 – 2 to 3<br>J21 – 2 to 3                 | J19 – 2 to 3<br>J18 – 2 to 3                 |  |  |

| PORT HW AS OUTPUT *                                     | J2 – 1 to 2                                        | J6 – 1 to 2                                        | J13 – 1 to 2                                       | J10 – 1 to 2                                       | J21–1 to 2                                   | J18-1 to 2                                   |  |  |

|                                                         |                                                    |                                                    |                                                    |                                                    |                                              |                                              |  |  |

| $GND_CLK = GND$                                         | J3 – 1 to 2                                        | J5 – 1 to 2                                        | J12 – 1 to 2                                       | J9 – 1 to 2                                        | J20 – 1 to 2                                 | J17 – 1 to 2                                 |  |  |

| GND_CLK = INPUT OR<br>OUTPUT *                          | J3 - 2  to  3<br>J4 - 1  to  2                     | J5 - 2  to  3<br>J8 - 1  to  2                     | J12 – 2 to 3<br>J15 – 1 to 2                       | J9 – 2 to 3<br>J16 – 1 to 2                        | J20 - 2  to  3<br>J23 - 1  to  2             | J17 - 2  to  3<br>J24 - 1  to  2             |  |  |

| GLOBAL CLK = INPUT *                                    | J4 – 2 to3                                         | J8 – 2 to3                                         | J15 – 2 to3                                        | J16 – 2 to3                                        | J23 – 2 to3                                  | J24 – 2 to3                                  |  |  |

|                                                         |                                                    |                                                    |                                                    |                                                    |                                              |                                              |  |  |

| CLAMP = EXT *                                           | J49 – 1 to 2                                       | J52 – 1 to 2                                       | J55 – 1 to 2                                       | J58 – 1 to 2                                       | J61 – 1 to 2                                 | J64 – 1 to 2                                 |  |  |

| CLAMP = +24V *                                          | J49 – 2 to 3<br>J50 – 1 to 2                       | J52 – 2 to 3<br>J53 – 1 to 2                       | J55 – 2 to 3<br>J56 – 1 to 2                       | J58 – 2 to 3<br>J59 – 1 to 2                       | J61 – 2 to 3<br>J62 – 1 to 2                 | J64 – 2 to 3<br>J65 – 1 to 2                 |  |  |

| CLAMP = +12V *                                          | J49 - 2  to  3<br>J50 - 2  to  3                   | J52 - 2  to  3<br>J53 - 2  to  3                   | J55 - 2  to  3<br>J56 - 2  to  3                   | J58 - 2  to  3<br>J59 - 2  to  3                   | J61 - 2  to  3<br>J62 - 2  to  3             | J64 - 2  to  3<br>J65 - 2  to  3             |  |  |

| CLAMP = +5V *                                           | J51 - 1  to  2<br>J49 - 2  to  3                   | J54 - 1 to 2<br>J52 - 2 to 3                       | J57 - 1  to  2<br>J55 - 2  to  3                   | J60 - 1  to  2<br>J58 - 2  to  3                   | J63 - 1  to  2<br>J61 - 2  to  3             | J66 - 1  to  2<br>J64 - 2  to  3             |  |  |

| $CLAIVIT = \pm 5 V^{-1}$                                | J49 = 2  to  3<br>J50 = 2  to  3<br>J51 = 2  to  3 | J52 - 2  to  3<br>J53 - 2  to  3<br>J54 - 2  to  3 | J55 - 2  to  3<br>J56 - 2  to  3<br>J57 - 2  to  3 | J58 = 2  to  3<br>J59 = 2  to  3<br>J60 = 2  to  3 | J61 - 2 to 3<br>J62 - 2 to 3<br>J63 - 2 to 3 | J64 - 2 to 3<br>J65 - 2 to 3<br>J66 - 2 to 3 |  |  |

#### TABLE 2-2: HARDWARE JUMPER CONFIGURATION

| HARDWARE JUMPERS INSTALLED (HW = HARD WIRED via JUMPER) |                                                    |                                                    |                                                    |                                                    |                                                    |                                                    |  |  |

|---------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|--|--|

| FUNCTION                                                | PORT 6                                             | PORT 7                                             | PORT 8                                             | PORT 9                                             | PORT 10                                            | PORT 11                                            |  |  |

| $GND_I/O = GND$                                         | J33 – 1 to 2                                       | J31 – 1 to 2                                       | J29 – 1 to 2                                       | J45 – 1 to 2                                       | J39 – 1 to 2                                       | J37 – 1 to 2                                       |  |  |